| Back | << | Index | >> |

objectifs

L’auto-pilotage des actionneurs électromécaniques triphasés nécessite la connaissance de

la position angulaire (angle électrique) du rotor.

Cette information est le plus souvent fournie par un « resolver » qui élabore un signal

sinusoïdal \(\alpha(t)\) où \(\alpha(t) = \Omega.t\) est

l’angle électrique.

A partir de là, une électronique fournit 3 sinusoïdes I.sin(Ωt), I.sin(Ωt - 2π/3) et I.sin(Ωt - 4π/3),

qui seront les consignes de courant instantané de chacune des phases.

Le « resolver » est un dispositif lui même électromécanique ou optique solidaire du rotor.

Il existe des situations particulières où des contraintes technologiques interdisent l’emploi d’un « resolver ».

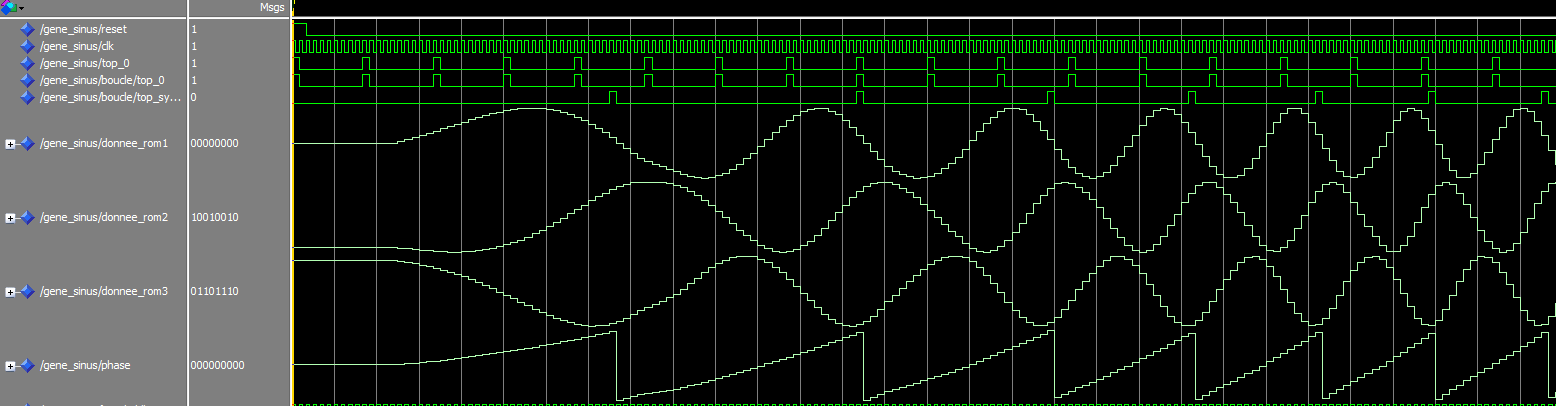

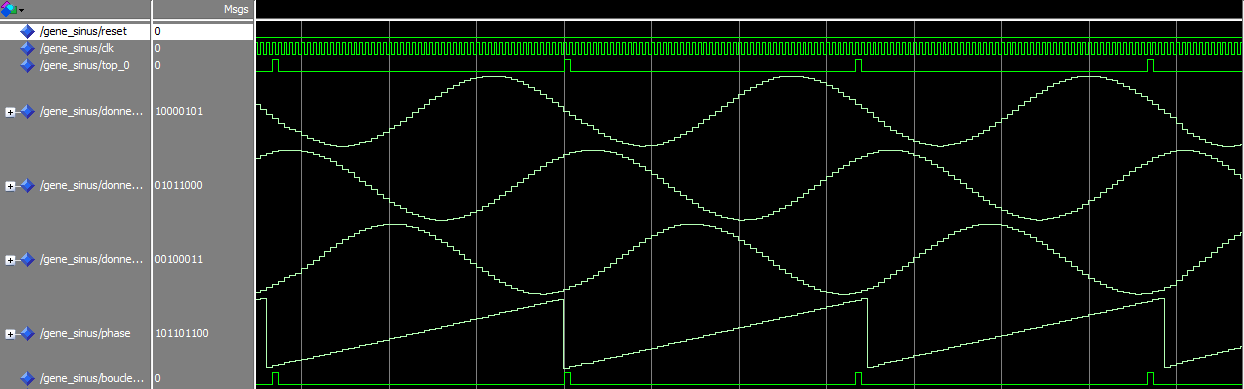

La seule information dont on dispose est une impulsion de « top 0 » à chaque passage de l’angle électrique par 0.

Il est alors nécessaire de reconstituer les 3 sinusoïdes à partir de cette impulsion, ce qui est la fonction de base

d’une boucle à verrouillage de phase (BVP).

On se propose d’étudier ici une boucle à verrouillage de phase entièrement numérique qui pourrait être implantée dans un circuit logique programmable de type FPGA :

Tous les circuits séquentiels de cette structure fonctionnent avec une même horloge de période Te

Le cahier des charges général est le suivant :

Dans tout le problème la fréquence de l’horloge est fixée à fe = 3 kHz

Démarage de la BVP pour une fréquence de 300 Hz :

Fonctionnement permanent pour une fréquence de 60 Hz :

Les ROMs ont chacune une capacité de \(2^{9}\) mots de 8 bits. On souhaite obtenir en sortie des sinusoïdes de dynamique maximum.

Donner pour chacune des 3 ROMs le contenu des 3 premières et des 3 dernières adresses

On propose un programme MATLAB pour générer les différents points de sinusoïde contenus dans les ROM :

Que faudra-t-il modifier dans ce programme pour générer les données des ROM 2 et 3 ?

INDICATION : Description d’une ROM en VHDL

La structure de cet OCN, organisée autour d’un additionneur et d’un registre N bits, est la suivante :

En prenant N=4, donner l’évolution de la phase numérique pour \(\delta\phi=1\) puis pour \(\delta\phi=3\) .

En déduire l’expression générale de la fréquence de la phase numérique en fonction de N, \(\delta\phi\)

Compte tenu du cahier des charges, déterminer la valeur minimum de N, et les valeurs de \(\delta\phi\) correspondant aux fréquences de 60 et 300 Hz.

Le comparateur de phases reçoit les signaux logiques « top 0 » et « top synchro ». Le rapport cyclique de ces signaux étant incertain,

il ne faudra prendre en compte que les fronts montants de ces signaux.

Le comparateur de phase élabore 2 signaux logiques AV et AR, actifs à l’état haut..

Le fonctionnement est le suivant :

On souhaite obtenir une impulsion d’une durée d’une période d’horloge lors du front montant du signal d’entrée.

On propose le diagramme d’états suivant :

On propose le diagramme d’états suivant pour décrire le fonctionnement du comparateur de phase :

Donner la succession des états dans les différents cas de figure et montrer que cela correspond au fonctionnement attendu

Le compteur/décompteur sera incrémenté (resp. décrémenté) au rythme de l’horloge si AV est actif (resp. AR actif).

Le correcteur a comme fonction de transfert \(4.5-4.25.z^{-1}\)

RAPPEL : Les calculs s’effectuent uniquement avec des nombres entiers ; une multiplication entre 2 entiers de taille N donne un résultat de taille 2*N.

| Back | << | Index | >> |